**Application Note**

# High Impedance Drivers During Power Failure Using XRT83SL3X/L3X LIU

### INTRODUCTION

For 1:1 or 1+1 line card redundancy in T1/E1 applications, power failure can cause a line card to change the characteristics of the line impedance, causing a degradation in system performance. EXAR's XRT83SL3X/L3X was designed to ensure reliability during power failures. The XRT83SL3X/L3x short-haul and long-haul line interface units (LIU) have patented high impedance circuits that allow the receiver inputs and the transmitter outputs to be Hi-Z when the LIU experiences a power failure or when the LIU is powered off. Note: For proper operation, a transformer must be used for coupling to the line.

#### TRANSMIT SECTION

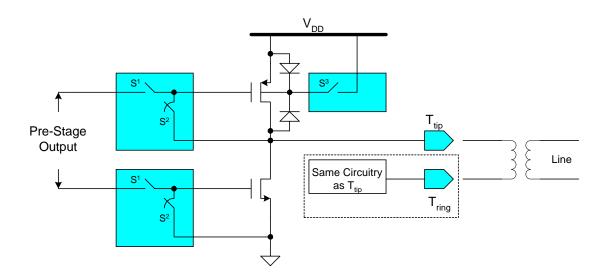

The transmitter outputs were designed so that during a power failure the transmitters will not load or short the active output drivers on other line cards. Figure 1 is a simplified block diagram of the transmitter output drivers of the XRT83SL3X/L3X. When a power failure occurs, switch S<sup>1</sup> is opened and the pre-stage output is disconnected from the gates of the transistors. Switch S<sup>2</sup> is closed, and switch S<sup>3</sup> determines the connectivity of the N-well to the transistors. When a power failure occurs, S<sup>3</sup> is opened disconnecting the N-well from the power supply, V<sub>DD</sub>. This allows the transmitters to be in high impedance mode when a power failure occurs.

Figure 1 Simplified Block Diagram of the Transmitter Output Drivers

#### **RECEIVE SECTION**

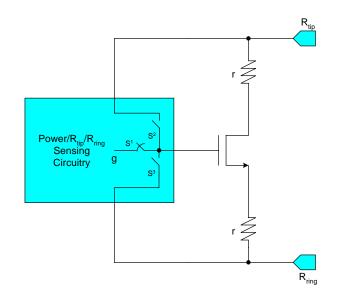

The receiver inputs were designed so that during a power failure the receivers will not load or short the active input drivers on other line cards. Figure 2 is a simplified block diagram of the receiver input drivers of the XRT83SL3X/L3X. The gate (g) of the transistor is controlled by a patented sensing circuit. The sensing circuit has two purposes. (1) The circuit senses the power supply and (2) senses  $R_{tip}$  and  $R_{ring}$ . In normal operation, S<sup>1</sup> is closed and S<sup>2</sup>, S<sup>3</sup> are opened. When a power failure occurs, S<sup>1</sup> opens causing g to be disconnected from the gate of the transistor. Depending on the values present on  $R_{tip}$  and  $R_{ring}$ , S<sup>2</sup> or S<sup>3</sup> will be closed allowing for the transistor to be turned off. For example: If  $R_{tip}$  is greater than  $R_{ring}$ , S<sup>3</sup> is closed and S<sup>2</sup> is opened. This allows an open path between  $R_{tip}$  and  $R_{ring}$  and provides for a high impedance node. The reverse is true when  $R_{ring}$  is greater than  $R_{tip}$ .

Figure 2 Simplified Block Diagram of the Receiver Inputs

## TEST DATA and LABORATORY SETUP

There are two critical measurements within the phylsical layer requirements that can determine whether the LIU causes system degradation from power failure, pulse template (transmitters) and bit errors (receivers). *Note: The following data was taken while toggling the power supplies On/Off.*

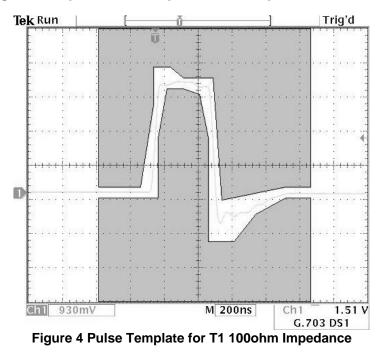

#### PULSE TEMPLATE

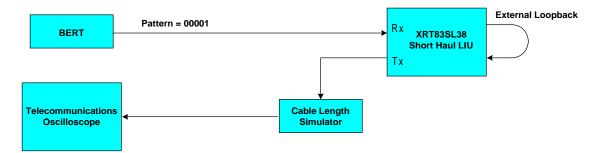

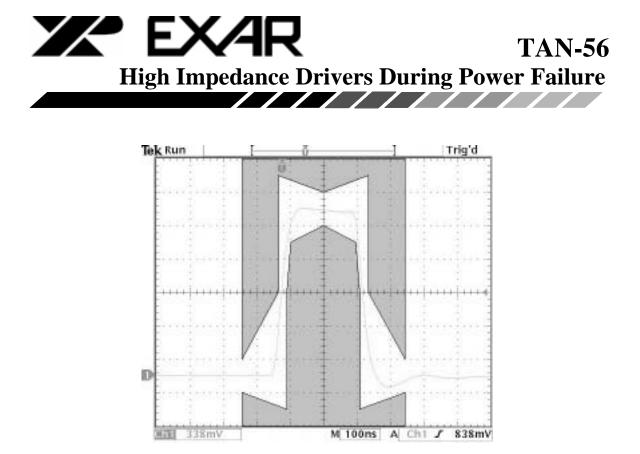

As with most physical layer requirements, T1 and E1 have different specifications to meet. However, the lab setup is very similar. Figure 3 is a simplified block diagram of the lab setup used to measure the pulse template of EXAR's XRT83SL38. The cable length simulator can be configured to test either T1 or E1 according to the value set from the control panel. For T1, the maximum cable loss specification is 655ft. For E1, the cable length is usually within 6ft. Figure 4 is a plot of the pulse template taken from the T1 setup. Figure 5 is a plot of the pulse template taken from the E1 setup.

Figure 3 Simplified Lab Setup for Pulse Template Measurements

Figure 5 Pulse Template for E1 75ohm Impedance

## **BIT ERRORS-RECEIVER INPUTS**

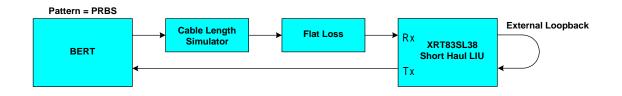

Bit errors are measured by inserting a psuedo random bit sequence to the receiver inputs of the primary card. The data is then sent back into the transmitter inputs from a system level loopback (external). Figure 6 is a simplified block diagram of the lab setup used to measure the receive sensitivity of EXAR's XRT83SL38. For short haul T1 applications, the maximum cable loss specification is 655ft of cable loss and 6dB of flat loss. For short haul E1 applications, the maximum cable loss specification is 6dB of cable loss and 12dB of flat loss. For both T1 and E1, the XRT83SL38 was able to receive signals attenuated up to 3,096ft of cable loss or 19dB of flat loss in the short haul mode.

## Figure 6 Simplified Lab Setup for Receive Sensitivity Measurements